强势插入 英特尔至强D处理器解析

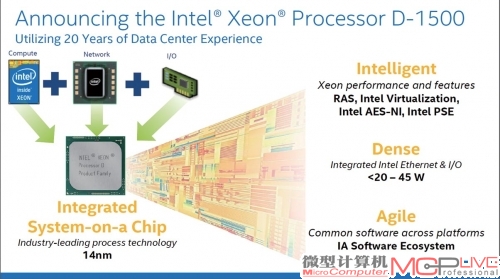

随着移动互联以及云服务的高速发展,对通信运营商和云服务提供商的数据中心提出了更高的要求。一直以来,寻求更低能耗成本和更高效的处理性能成为行业用户的新需求,所以近期英特尔发布了全新的至强D系列产品。该系列特别针对网络设备和运营商而设计,实际性能介于至强E5和凌动C2000系列之间,但它的独特之处在于,这是首款基于至强的SoC芯片,而且采用14nm制程生产,在具备出色低功耗特性的同时,拥有较为不错的性能表现。

至强D系列处理器问世

此次英特尔率先推出的至强D处理器包括两款产品—D-1540和D-1520,其中D-1540拥有8核心16线程,主频2.0GHz。D-1520拥有4核8线程,主频2.2GHz。两者的TDP功耗均为45W,并且大睿频均为2.6GHz。

英特尔的处理器发展一直遵循“Tick-Tock”周期,Tick代表全新制程更新,Tock代表微架构更新。英特尔在2013年推出代号“Haswell”全新架构CPU,但仍然基于22nm制程;在2014年将制程继续推进到14nm,也就是代号“Broadwell”的产品。“Broadwell”早见于去年9月份推出的Core M系列处理器,在今年的CES上则大放光彩,英特尔共推出了17款Broadwell-U处理器。按照其以往的产品发布进度来看,服务器端的产品基本上会晚于桌面端一代,但3月份就推出的至强D处理器可算是打破了这一规律。这是英特尔首个14nm级的服务器核心,不但几乎同步采用了先进的制造工艺,让其TDP功耗仅在20W~45W之间,而且还是首款基于至强的SoC产品。对于同时追求低功耗和性能的运营商和网络服务商而言,在动态Web服务、专用托管和Web高速缓存为主的超大规模轻量型工作负载,以及公有云、暖存储等领域都会有它的用武之地。

真正的至强级内核结构

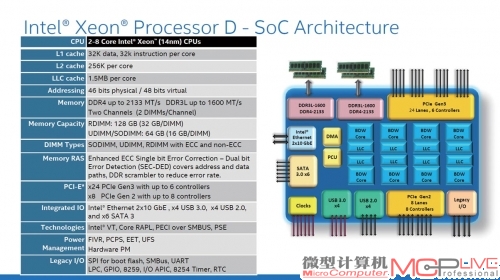

至强D处理器设计为高8个Broadwell核心,每个Broadwell内核本身又包含一个32KB数据高速缓存及一个32KB指令高速缓存,还有一个256KB的二级共享高速缓存,以及1.5MB的末级高速缓存(LLC Cache),末级高速缓存总容量为12MB,并且在所有内核之间还可以共享。该核心还支持超线程技术,即可以支持16线程。所以,至强D的核心和其它至强处理器是相同级别的,这在性能方面就比之前针对低功耗服务器市场的凌动C2000系列拥有较大的优势,而且能够提供至强级别的功能。

由于这一代Broadwell主要是更新制造工艺,其内核架构仍然基于Haswell,因此至强D与至强E系列处理器在所有虚拟化技术、功耗管理RAPL、SMBus PACI接口以及平台存储扩展等方面均保持相同。

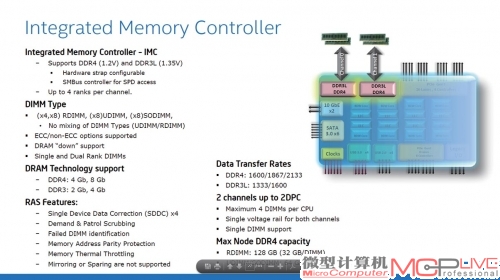

内存支持能力比凌动C2000强

在内存控制器方面,它虽然比之前的至强有所缩减,比如只有两个内存控制器,支持双通道内存,四个DIMMs,支持伸缩式128GB可寻址内存。但内存支持却很全面,不但支持DDR3L和新的DDR4内存规格,而且SODIMM、UDIMM、RDIMM等内存种类都支持。

英特尔D处理器拥有双内存控制器,支持DDR3L和DDR4内存。

至强D处理器还支持ECC和非ECC,提供RAS特性,包括一位纠错和双位纠错,同时处理器和DRAM之间具有地址和数据路径纠错的特性,并且对于DDR4,至强D处理器还会使用其他技术,通过置乱来减少错误率。借助DDR4,目前的DIMM技术可以提供两种新功能,一种功能是命令地址模仿,它在Haswell和Broadwell至强D处理器系列产品中均提供。除了该功能,所有的DDR4 DIMM还支持适当的CRC检查,旨在防止写入时出现的错误传播到磁盘,这一功能也在至强D处理器上被使用,以提高使用DDR4技术的容错率。此外,英特尔还在至强D处理器的PCI-E I/O子系统中添加了ECRC保护,支持对CRC包进行微处理,我们可以将包中的CRC信息从设备上直接传送至根组件(Root Complex),而且它会随CRC全程全面保护PCI-E数据以上传的方式通过I/O子系统。

不过在这一代产品上,英特尔并未部署和验证某些更高级的特性,如英特尔高端产品上的镜像和备用特性。

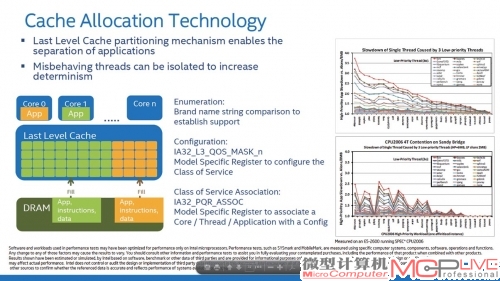

至强D的内存控制器仍然是服务器级的,叫做本地代理内存控制器复合体HAMC。它通过双向环形总线连接高速缓存和内核部分。连接了8个Broadwell内核及8个末级高速缓存片。该环形总线是一种并行架构,每个内核搭配一个高速缓存片,形成一种物理组织。同时,LLC末级缓存在所有内核间共享,每个高速缓存代表一个独立的处理管道。在这一特定配置中,末级高速缓存支持一次处理多达8个并发请求。并且,整个处理过程是处于智能调控状态,在正常情况下,所有8个内核可以访问整个高速缓存、分布式高速缓存及末级高速缓存,并且动态调配内核访问高速缓存区。可以获得较高的命中率,并直接通过用于连接内核及内存系统的高带宽传输环将数据返回至内核。